# Xilinx FPGA 的 power-up 配置和 start-up 过程

FPGA 的配置分为 3 步,

- 1. 清除配置 SRAM

- 2. 下载配置数据

- 3. Start-up 过程激活逻辑

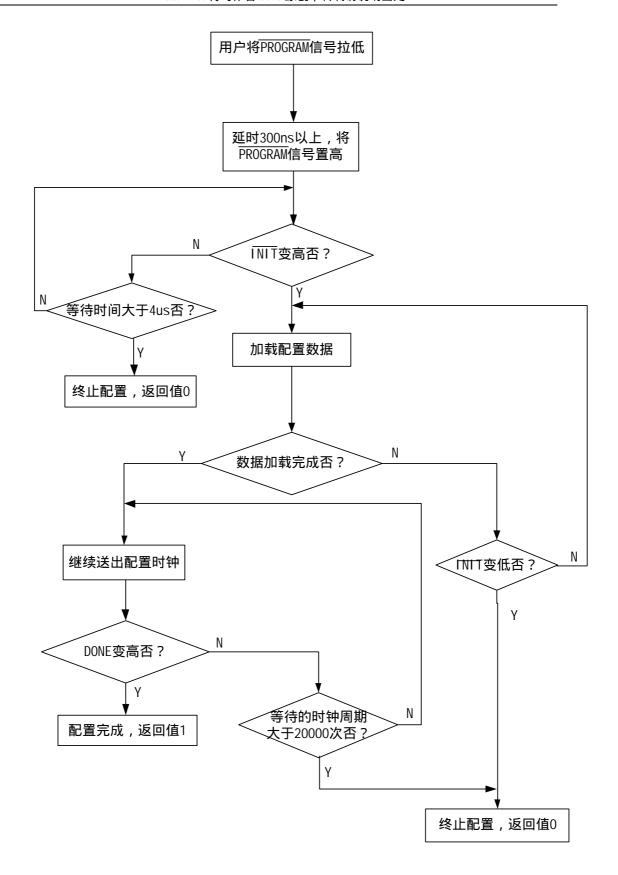

igure 14: Serial Configuration Flowchart

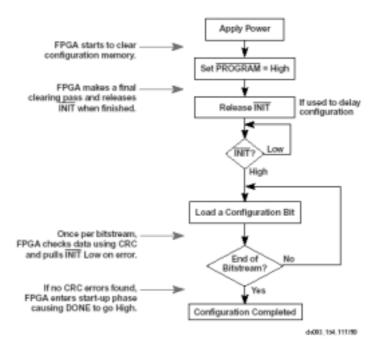

# Power-up 配置

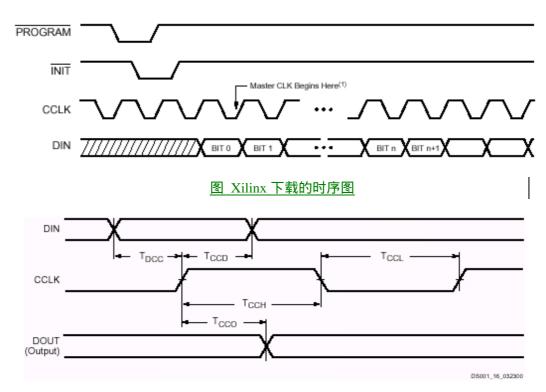

从上图可见,配置在 FPGA 上电时自动进行。上电后,FPGA 自动开始清楚 RAM 的内容(此时,外围电路应使/program=1),清除 RAM 后,FPGA 使/INIT 变为无效,开始装载配置 bit(如果保持/INIT 信号有效,则可以延迟装载 bit,INIT 是双向端口)。装载 bit 的过程中,FPGA 会做 CRC 检查,发现错误则把/INIT 信号拉低。配置完成后 done 变高。配置时序如下图所示。

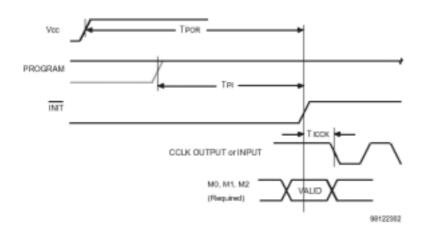

Figure 19: Power-up Timing Configuration Signals

也可以通过把/program 置低开始(在不重新上电的情况下开始配置 FPGA)

对 Xilinx FPGA 的配置有四个主要步骤(不重新上电的情况下开始配置 FPGA):

## (1) 配置存储器清空(Clearing Configuration Memory)

将 PROGRAM 管脚拉低 300ns 以上。当 PROGRAM 拉低后,开始配置存储器,将存储器清空。此时 INIT 将被拉低,当 PROGRAM 置高后,FPGA 将继续将 INIT 置低直到完全清除完所有的配置存储器。当 INIT 变高时,配置便可以开始了。

# (2) 加载配置数据 (Loading Configuration Data)

当 INIT 变高时,便可以配置 FPGA 了。配置时,先将 CCLK 置低,再将数据发送到 DIN上,延时 45ns 以上,再将 CCLK 置高,该位数据便写入到了 FPGA 中(数据是低位在前),然后再准备下一次的输入。如此反复,将所有数据输入完毕为止。

## (3) CRC 错误校验 (CRC Error Checking)

在加载数据过程中,嵌入到配置文件中的 CRC 值同 FPGA 计算出来的值比较,若有 CRC 校验错误产生,则 INIT 置低,且 FPGA 停止加载。

## Start-up 过程

默认的 start-up 过程在 DONE 信号变高并延迟一个 CCLK 后进行,此时 global tri-state signal(GTS)信号释放,这样允许器件 output 打开。

一个 CCLK 后, Global Set/Reset (GSR)和 Global Write Enable (GWE)信号释放,这

样允许内部储存元件开始随着逻辑和用户时钟做出反应。

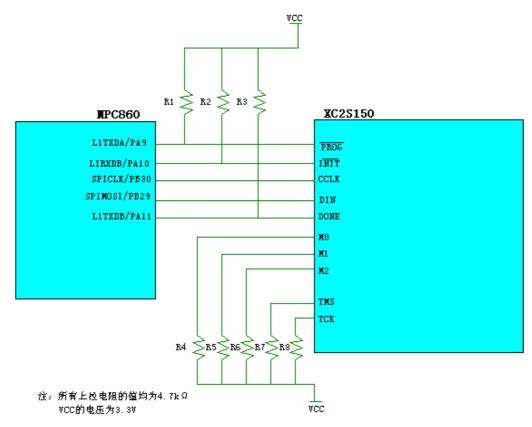

#### 用 CPU 配置 FPGA

• ♥ 图 1 MPC860与 XC2S150的 Slave Serial模式的连接示意图+

## 4.2.7 采用 Slave Serial 模式对单个 FPGA 进行配置

在 Slave Serial 模式中,需要将"MO、M1、M2"设置为"111"。

对 Xilinx FPGA 的配置有四个主要步骤:

## (4) 配置存储器清空(Clearing Configuration Memory)

将 PROGRAM 管脚拉低 300ns 以上。当 PROGRAM 拉低后,开始配置存储器,将存储器清空。此时 INIT 将被拉低,当 PROGRAM 置高后,FPGA 将继续将 INIT 置低直到完全清除完所有的配置存储器。当 INIT 变高时,配置便可以开始了。

# (5) 加载配置数据 (Loading Configuration Data)

当 INIT 变高时,便可以配置 FPGA 了。配置时,先将 CCLK 置低,再将数据发送到 DIN上,延时 45ns 以上,再将 CCLK 置高,该位数据便写入到了 FPGA 中(数据是

低位在前),然后再准备下一次的输入。如此反复,将所有数据输入完毕为止。

## (6) CRC 错误校验 (CRC Error Checking)

在加载数据过程中,嵌入到配置文件中的 CRC 值同 FPGA 计算出来的值比较,若有 CRC 校验错误产生,则 INIT 置低,且 FPGA 停止加载。

## (7) FPGA 开始运行(Start-up)

数据加载完毕后,继续送出 CCLK 时钟,等待 DONE 置高。当 DONE 置高后,FPGA将进入 Start-up 状态,即 FPGA 从配置状态转入到运行状态。

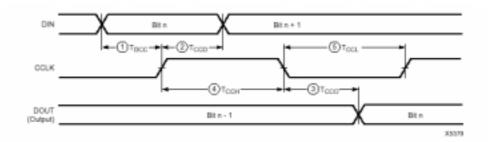

Xilinx FPGA 的下载时序图如图所示。

| Symbol           |          | Description       |    | Units    |  |

|------------------|----------|-------------------|----|----------|--|

| T <sub>DCC</sub> | - CCLK - | DIN setup         | 5  | ns, min  |  |

| T <sub>CCD</sub> |          | DIN hold          | 0  | ns, min  |  |

| T <sub>CCO</sub> |          | DOUT              | 12 | ns, max  |  |

| T <sub>CCH</sub> |          | High time         | 5  | ns, min  |  |

| T <sub>CCL</sub> |          | Low time          | 5  | ns, min  |  |

| F <sub>CC</sub>  |          | Maximum frequency | 66 | MHz, max |  |

图 Virtex、Virtex –e 和 Spartan Slave Serial 模式的时间关系图

|      | Description |   | Symbol           | Min | Max | Units |

|------|-------------|---|------------------|-----|-----|-------|

| CCLK | DIN setup   | 1 | TDCC             | 20  |     | ns    |

|      | DIN hold    | 2 | T <sub>CCD</sub> | 0   |     | ns    |

|      | DIN to DOUT | 3 | Tooo             |     | 30  | ns    |

|      | High time   | 4 | Tooh             | 45  |     | ns    |

|      | Low time    | 5 | T <sub>CCL</sub> | 45  |     | ns    |

|      | Frequency   |   | Foc              |     | 10  | MHz   |

Note: Configuration must be delayed until the INIT pins of all daisy-chained FPGAs are High.

#### 图 SpartanXL Slave Serial 模式的时间关系图

#### 其操作过程如下所述:

CPU 按下列步骤操作 I/O 口线,即可完成对 FPGA 的配置:

- 1.设置 PROGRAM = '0', 保持 300ns 以上, 然后再设置 PROGRAM = '1'。

- 3.置 CCLK= "0", DIN 上放置数据(低位在前), 延时(45ns以上)。

- 4. CCLK="1"(将数据写入 FPGA 中), 并延时 45ns 以上, 并检测 INIT 是否变低, 若 INIT = '0', FPGA 需要重新配置。

- 5.准备下一位数据,并重复执行步骤3、4,直到所有数据送出为止。

- 6.继续送出时钟信号,并等待 DONE 置高。当 DONE 置高后,表明 FPGA 的配置已完成。若在一定时钟周期内 DONE 不能置高(需要等待的最大时钟周期在 DataSheet中没有介绍,Xilinx 的技术人员说是配置成功一般需要十几个时钟周期 DONE 信号便会抬高,在例程和流程图中,我们采用了等待 20000 个时钟周期,此时 DONE 还不置高,表示配置异常。),必须重新配置(从步骤 1 开始)。

#### 其配置流程图如下图所示: